# PC-104-AO-001 Dual Channel Analog Output Module

# Contents

| Introduction                 | 3  |

|------------------------------|----|

| Features                     | 3  |

| Specification                | 3  |

| Location Diagram             | Ę  |

| Base I/O Port Address        |    |

| Jumper Setting               | 8  |

| Connector Pin Assignments    | 10 |

| Programming Reference        |    |

| Output Connections           | 13 |

| Channel 1 Output Adjustments | 14 |

| Channel 2 Output Adjustments | 15 |

|                              |    |

#### Introduction

The PC104-AO-001 is a PC104 Analog Output module. It contains two analog output channels which can be configured independently for voltage or current output. Each channel is individually user selectable to any of the following ranges: 0 to 5V, 0 to 10V, -2.5V to +2.5V, -5V to +5V, -10V to +10V or 4mA to 20mA outputs.

#### **Features**

- □ 2 channel analog output

- $\Box$  0V to 5V, 0V to 10V,  $\pm 2.5$ V,  $\pm 5$ V,  $\pm 10$ V and 4mA to 20mA output range

- □ 15 bit resolution

- □ High speed

- Arr PC104 Standard +5V, ±12V power supply

### **Specification**

#### **Analog Output**

Number channel 2

Output voltage range

Unipolar 0~5V, 0~10V

Bipolar  $\pm 2.5V, \pm 5V, \pm 10V$

Output current range 4mA to 20mA

Voltage output current range  $\pm 5 \text{mA}$ Source impedence  $0.1\Omega$  max.

#### **Accuracy**

Resolution 15 bits Nonlinearity ±4LSB Differential nonlinearity ±4LSB

System Accuracy 0.012% FSR (Voltage Output)

0.05% FSR (Current Output)

#### **Dynamic Performance**

Settling Time to ±0.003%FSR

$\begin{array}{ll} 1LSB \ output \ step & 4\mu s \\ Slew \ Rate & 10V/\mu s \end{array}$

#### **Thermal Cheracteristic**

Zero Drift  $\pm 0.7 \mu V/^{\circ}C$

Gain Drift  $\pm 3\sim 20$ ppm of FSR

#### **Power Requirements**

$+5V, \pm 12V$

Loop Supply Voltage 7.5V to 36V DC

Max power dissipation 3.8W

#### **Physical/Environmental**

I/O Connector 10 pin male connector

Dimensions 3.775" x 3.55"

Weight 70-grams Operating Temperature Range  $0 \sim 70 \,^{\circ}\text{C}$  Storage Temperature Range  $0 \sim 70 \,^{\circ}\text{C}$

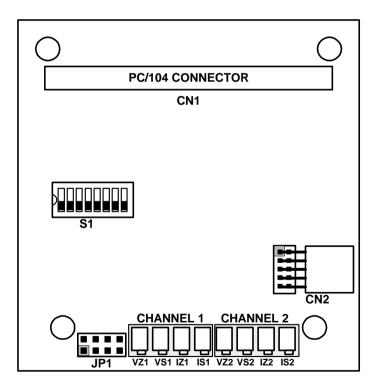

#### **LOCATION DIAGRAM**

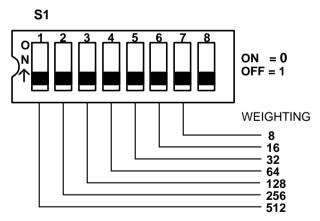

#### Base I/O Port Address

The PC104-AO-001 module occupies 8 consecutive locations in I/O address space. If more than one module is to be installed to the embedded system, each module must be given its own distinct I/O address or base address. No more than one module may use the same base address. The I/O Port address or base address for a particular module is can be configured by using the Dip-Switch (S1). To set to appropriate base address, switch the individual switches into the ON or OFF position.

The default base address setting for the PC104-AO-001 module is 3F8 (Hex) and is shown below.

#### **Base Address Setting**

Each switch represents one address weight. The desired base address is determined by adding the weight of the switches.

The base address calculation is as shown below.

| I/O PORT<br>RANGE | DIP SWITCH POSITION |    |    |           |    |    |           |   |  |

|-------------------|---------------------|----|----|-----------|----|----|-----------|---|--|

| TT d:1            | 1                   | 2  | 3  | 4         | 5  | 6  | 7         | 8 |  |

| Hexadecimal       | <b>A9</b>           | A8 | A7 | <b>A6</b> | A5 | A4 | <b>A3</b> | X |  |

| 200 - 207         | 1                   | 0  | 0  | 0         | 0  | 0  | 0         | X |  |

| 208 - 20F         | 1                   | 0  | 0  | 0         | 0  | 0  | 1         | X |  |

| 210 - 217         | 1                   | 0  | 0  | 0         | 0  | 1  | 0         | X |  |

| 218 - 21F         | 1                   | 0  | 0  | 0         | 0  | 1  | 1         | X |  |

| 220 - 227         | 1                   | 0  | 0  | 0         | 1  | 0  | 0         | X |  |

| -                 | -                   | -  | -  | -         | -  | -  | -         | - |  |

| -                 | -                   | -  | -  | -         | -  | -  | -         | - |  |

| -                 | -                   | -  | -  | -         | -  | -  | -         | - |  |

| 3F0 - 3F7         | 1                   | 1  | 1  | 1         | 1  | 1  | 0         | X |  |

| (*) 3F8 - 3FF     | 1                   | 1  | 1  | 1         | 1  | 1  | 1         | X |  |

$$0 = ON$$

,  $1 = OFF$ ,  $(*) = Default Setting$

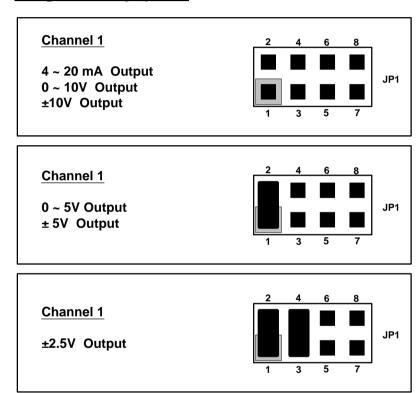

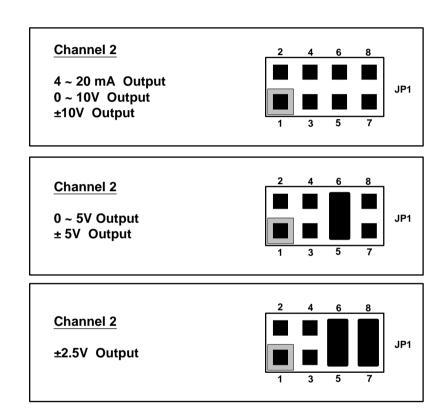

## Jumper Setting of JP1

## Jumper Setting of JP1

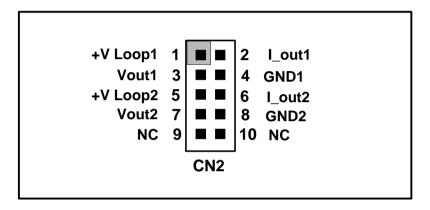

## Connector Pin Assignments (CN2)

| PIN No<br>of CN2 | PIN<br>NAME | DESCRIPTION                   |

|------------------|-------------|-------------------------------|

| 1                | +V Loop1    | Channel 1 Loop Supply Voltage |

| 2                | I_out1      | Channel 1 Current Output      |

| 3                | Vout1       | Channel 1 Voltage Output      |

| 4                | GND1        | Channel 1 Ground              |

| 5                | +V Loop2    | Channel 2 Loop Supply Voltage |

| 6                | I_out2      | Channel 2 Current Output      |

| 7                | Vout2       | Channel 2 Voltage Output      |

| 8                | GND2        | Channel 2 Ground              |

| 9                | NC          | No Connection                 |

| 10               | NC          | No Connection                 |

#### **Programming Reference**

PC104-AO-001 analog output module is especially designed for 4 to 20mA analog output application. The module consists of two 16-bit D/A channels and are designed to accept positive-true binary two's completement (BTC) input codes which are compatible with bipolar analog output operation.

The method of transferring the input data to each D/A converter is as follow.

The module is designed to accept the Lower 8-bits of the First channel at the *Base address* and then the Higher 8-bits of the First channel is at the address of *Base address* + 1. Then the Lower 8-bits of the Second channel is at *Base address* + 2 and the Higher 8-bits of the Second channel is to be written at the address of *Base address* + 3. Both of D/A converters output will be enabled and updated when the address of *Base address* + 4 is sent.

It is necessary to calibrate whenver the output configuration is made changes.

For Unipolar operation and 4 to 20mA Current output operation, the input code should be  $7FFF_H$  as Full Scale and  $0000_H$  as Zero.

For *Bipolar analog output configuration*, the following table shows the digital input codes and their related analog output voltages respectively.

| DIGITAL INPUT<br>CODE<br>BINARY TWO'S<br>COMPLEMENT BTC | ANALOG<br>OUTPUT<br>(V) | DESCRIPTION        |  |  |

|---------------------------------------------------------|-------------------------|--------------------|--|--|

| 7FFF <sub>H</sub>                                       | +9.999695               | +Full Scale – 1LSB |  |  |

| <br>4000 <sub>н</sub><br>                               | +5.000000<br>           | ³¼ Scale           |  |  |

| 0001 <sub>H</sub>                                       | +0.000305               | BPZ + 1LSB         |  |  |

| 0000 <sub>H</sub>                                       | 0.000000<br>I           | Bipolar Zero (BPZ) |  |  |

| FFFF <sub>H</sub>                                       | -0.000305               | BPZ – 1LSB         |  |  |

| С000 <sub>н</sub>                                       | -5.000000<br>           | 1/4 Scale          |  |  |

| 8000 <sub>H</sub>                                       | -10.000000              | Minus Full Scale   |  |  |

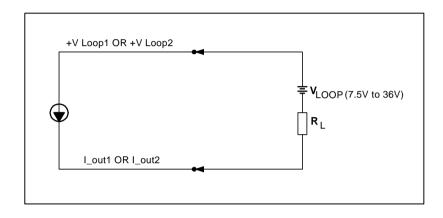

## **Current Output Connection Diagram**

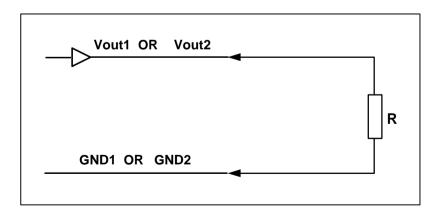

## **Voltage Output Connection Diagram**

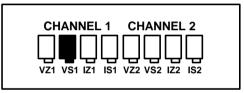

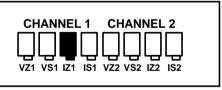

#### Channel 1 Voltage and Current Output Adjustments

VZ1 = Voltage Output Zero Adjustment for Channel 1.

CHANNEL 1 CHANNEL 2

VZ1 VS1 IZ1 IS1 VZ2 VS2 IZ2 IS2

VS1 = Voltage Output Span Adjustment for Channel 1.

IZ1 = Current Output Zero Adjustment for Channel 1.

**IS1** = Current Output Span Adjustment for Channel 1.

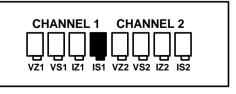

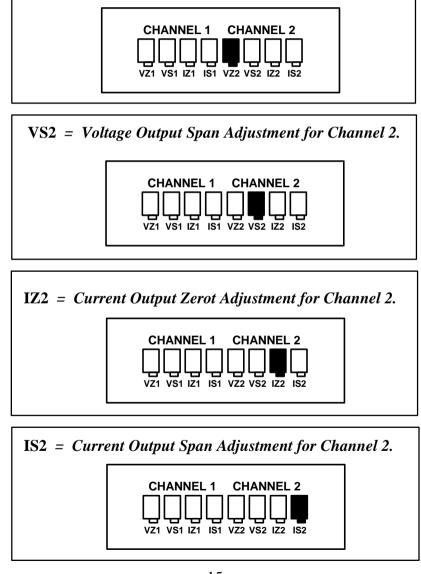

#### Channel 2 Voltage and Current Output Adjustments

VZ2 = Voltage Output Zero Adjustment for Channel 2.

## Notes